Thesis for the degree of Licentiate of Engineering

## Obsidian: GPU Kernel Programming in Haskell

Joel Svensson

**CHALMERS** | GÖTEBORG UNIVERSITY

Department of Computer Science and Engineering Chalmers University Of Technology and Göteborg University Göteborg, Sweden 2011

## Obsidian: GPU Kernel Programming in Haskell

Joel Svensson

© 2011 Joel Svensson

Technical Report 77L ISSN 1652-876X Department of Computer Science and Engineering Functional Programming Research Group

Chalmers University of Technology and Göteborg University SE–412 96 Göteborg, Sweden Phone: +46 (0)31–772 1000

Printed in Sweden Chalmers Reproservice Göteborg, Sweden 2011

### Abstract

Graphics Processing Units (GPUs) are evolving into powerful general purpose computing platforms. At first, GPU performance was driven by the requirements of 3D graphics computer games. To fit this workload, a GPU is a many-core processor suitable for the data-parallel programming paradigm. Today, GPUs come with hundreds of processing elements and a theoretical single precision floating point performance in the teraflop range.

Because of the computing power of modern GPUs, programmers are increasingly interested in making use of them for non-graphics applications. This desire has given rise to the research field that studies General Purpose Computations on GPUs (GPGPU). The manufacturers of GPUs are also acknowledging this trend and are tailoring their GPUs to meet both the desires of those playing games and the GPGPU community.

CUDA is NVIDIA's tool-set for GPGPU programming on their GPUs. CUDA is a big improvement for the GPGPU programmer compared to what was available before. In the early days, the GPGPU programmer was forced to express the algorithm being implemented as a computer graphics computation. CUDA provides a C compiler and a set of libraries for general purpose programming on the GPU, freeing the programmer from graphics APIs. In CUDA, the programmer decomposes the problem into a set of kernels. A kernel is an isolated data-parallel program executed by a number of threads on the GPU. CUDA has some problems. For example, CUDA is a very low level interface to the GPU capabilities and there is also the issue that CUDA kernels are not easily composable.

Obsidian is an embedded language for implementing kernels in the functional programming language Haskell. From higher level descriptions of algorithms based on combinators, CUDA code is generated. Using this approach, Obsidian kernels are more compositional and also relieve the programmer from inventing the typically complex index arithmetic expressions that are used to load and store data in data-parallel algorithms. The indexing arithmetic is hidden away from the programmer in the set of combinators provided as a library.

The performance obtained from the kernels generated using Obsidian is decent. It does not compare to optimized handwritten code but if the implementation effort is taken into consideration performance is good. Obsidian allows the programmer to think about the problem at hand, rather than being weighed down by the lower level details.

In this thesis, two different implementations of Obsidian are shown. The first of these implementations is based on monads and the second on arrows, two concepts familiar to functional programmers. A number of applications are presented, expressed using the arrow based version.

## Acknowledgments

I extend thanks to my supervisor Mary Sheeran, for her support, insights and motivational abilities. I also thank her very much for reading this thesis many times and pointing out all those typically Swedish mistakes I have made while writing. I would also like to thank my co-supervisor Koen Claessen for all the technical help he has offered during the work leading up to this thesis. Without Koen's help and input, this thesis would not have been possible.

Thanks also go to the "graphics guys", Erik Sintorn, Markus Billeter and Ola Olsson. We do not meet often but I always enjoy our encounters very much. Their insights into graphics processor architecture and programming is a valuable source of information. I learn something new each time we meet. I also thank their supervisor, Ulf Assarsson, for giving awesome graphics courses and also being very helpful with graphics processor related questions.

Thanks to my room-mates Nicholas Smallbone and Michal Palka and to colleagues Anders Persson and Emil Axelsson. They are all intriguing persons with large wells of knowledge that I wish I could tap into more often.

Sean Lee and Trevor McDonell, both at the University of New South Wales when I first met them, had many interesting suggestions and comments about Obsidian. Some of their suggestions found their way into the implementation. Sean and Trevor are people I have often turned to with technical questions.

Thanks to everyone at the computer science and engineering department at Chalmers for creating a pleasant work atmosphere.

Finally, and most importantly thanks to my wife for being so supportive of my endeavors. She is very patient with my occasionally awkward working hours.

This research is funded by the Swedish Research Council.

ii

## Publications

This thesis is based on the work previously published as:

- GPGPU kernel implementation and refinement using Obsidian [36] Published 2010 in Procedia Computer Science.

- Obsidian: A Domain Specific Embedded Language for General-Purpose Parallel Programming of Graphics Processors [38] To appear in Springer Lecture Notes in Computer Science (nr: 5836).

- GPGPU Kernel Implementation using an Embedded Language: a Status Report [37]. Published 2010, technical report 2010:1 Dept. of Computer Science and Engineering, Chalmers University of Technology.

iv

# Contents

| 1                                       | $\operatorname{Intr}$ | roduction                                                                                                                                        | 1        |

|-----------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                         | 1.1                   | Graphics Processing Unit: Supercomputer on a PCIe card $\ldots$                                                                                  | 1        |

| 1.2 Obsidian: Embedded language for GPU |                       |                                                                                                                                                  |          |

|                                         |                       | $computing \ldots \ldots$ | 2        |

|                                         | 1.3                   | Research questions                                                                                                                               | 2        |

|                                         | 1.4                   | Structure of this thesis                                                                                                                         | 2        |

| <b>2</b>                                | Gen                   | neral purpose computations on GPUs                                                                                                               | <b>5</b> |

|                                         | 2.1                   | Introduction                                                                                                                                     | 5        |

|                                         | 2.2                   | NVIDIA CUDA                                                                                                                                      | 5        |

|                                         |                       | 2.2.1 CUDA architecture                                                                                                                          | 6        |

|                                         |                       | 2.2.2 CUDA programming model                                                                                                                     | 7        |

|                                         |                       | 2.2.3 CUDA programming example                                                                                                                   | 9        |

|                                         |                       | 2.2.4 Conclusions $\ldots$                                      | 13       |

|                                         | 2.3                   | Other GPGPU programming languages                                                                                                                | 14       |

|                                         |                       | 2.3.1 OpenCL                                                                                                                                     | 14       |

| 3                                       | $\mathbf{Em}$         | bedded domain specific languages                                                                                                                 | 17       |

|                                         | 3.1                   | Introduction                                                                                                                                     | 17       |

|                                         | 3.2                   | Abstract syntax                                                                                                                                  | 18       |

|                                         | 3.3                   | Syntax                                                                                                                                           | 18       |

|                                         | 3.4                   | Inlining                                                                                                                                         | 19       |

#### CONTENTS

|   | 3.5             | Optimization and smart constructors                                                        |

|---|-----------------|--------------------------------------------------------------------------------------------|

|   | 3.6             | Conclusion                                                                                 |

| 4 | Obs             | idian 21                                                                                   |

|   | 4.1             | Introduction                                                                               |

|   | 4.2             | Array language                                                                             |

|   | 4.3             | Notes on recursion                                                                         |

|   | 4.4 GPU kernels |                                                                                            |

|   |                 | 4.4.1 Pure                                                                                 |

|   |                 | 4.4.2 Execute                                                                              |

|   |                 | 4.4.3 Sequential composition                                                               |

|   |                 | 4.4.4 Sync                                                                                 |

|   |                 | 4.4.5 Sync and parallelism                                                                 |

|   |                 | 4.4.6 Sync and sequentiality                                                               |

|   |                 | 4.4.7 Divide and conquer                                                                   |

|   | 4.5             | List of contributions                                                                      |

|   |                 | 4.5.1 Compositionality $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 48$ |

|   |                 | 4.5.2 Combinators for parallel programming                                                 |

|   |                 | 4.5.3 Data/work partitioning                                                               |

|   |                 | 4.5.4 Indexing computations                                                                |

| 5 | Imr             | lementation 51                                                                             |

| 0 | 5.1             | Expressions                                                                                |

|   |                 | Array language                                                                             |

|   | 5.3             | The monadic approach                                                                       |

|   | 0.0             | 5.3.1 Pure                                                                                 |

|   |                 | 5.3.2 Sync                                                                                 |

|   |                 | 5.3.3 Sequential composition                                                               |

|   |                 | 5.3.4 The two combinator                                                                   |

|   |                 | $5.5.4  \text{inc two combinator}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  0 \\$  |

|   |                                                                             | 5.3.5                                                             | Code generation                                                                                                                                                                                                                 | 65                                                 |

|---|-----------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   | 5.4                                                                         | The a                                                             | rrow based approach                                                                                                                                                                                                             | 69                                                 |

|   |                                                                             | 5.4.1                                                             | Pure                                                                                                                                                                                                                            | 70                                                 |

|   |                                                                             | 5.4.2                                                             | Sync                                                                                                                                                                                                                            | 70                                                 |

|   |                                                                             | 5.4.3                                                             | Sequential composition                                                                                                                                                                                                          | 71                                                 |

|   |                                                                             | 5.4.4                                                             | The two combinator                                                                                                                                                                                                              | 71                                                 |

|   |                                                                             | 5.4.5                                                             | Optimization of expressions                                                                                                                                                                                                     | 75                                                 |

|   |                                                                             | 5.4.6                                                             | Code generation                                                                                                                                                                                                                 | 79                                                 |

|   |                                                                             | 5.4.7                                                             | Sidetrack                                                                                                                                                                                                                       | 83                                                 |

|   | 5.5                                                                         | Comp                                                              | arison of the two implementations                                                                                                                                                                                               | 85                                                 |

|   | 5.6                                                                         | Future                                                            | e work                                                                                                                                                                                                                          | 86                                                 |

|   |                                                                             |                                                                   |                                                                                                                                                                                                                                 |                                                    |

| 6 | $\mathbf{Cas}$                                                              | se studies                                                        |                                                                                                                                                                                                                                 |                                                    |

| - |                                                                             |                                                                   |                                                                                                                                                                                                                                 |                                                    |

| - | 6.1                                                                         | Reduc                                                             | tion $\ldots$                                                                                                                                                                                                                   |                                                    |

| - | 6.1<br>6.2                                                                  |                                                                   |                                                                                                                                                                                                                                 | 89<br>91                                           |

| - | -                                                                           | Dot p                                                             | $\operatorname{roduct}$                                                                                                                                                                                                         | 89                                                 |

|   | 6.2                                                                         | Dot pr<br>Merge                                                   | roduct                                                                                                                                                                                                                          | 89<br>91                                           |

|   | 6.2<br>6.3                                                                  | Dot pr<br>Merge<br>Sortin                                         | roduct                                                                                                                                                                                                                          | 89<br>91<br>94                                     |

|   | <ul><li>6.2</li><li>6.3</li><li>6.4</li></ul>                               | Dot pr<br>Merge<br>Sortin<br>Paralle                              | roduct                                                                                                                                                                                                                          | 89<br>91<br>94<br>00                               |

|   | <ul><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul>                   | Dot pr<br>Merge<br>Sortin<br>Paralle<br>Paralle                   | roduct                                                                                                                                                                                                                          | 89<br>91<br>94<br>00<br>02                         |

|   | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul> | Dot pr<br>Merge<br>Sortin<br>Paralle<br>Paralle                   | roduct       9         rs       9         g networks       10         el prefix       10         el prefix       10         on performance       10                                                                             | 89<br>91<br>94<br>00<br>02<br>06<br>08             |

|   | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul> | Dot pr<br>Merge<br>Sortin<br>Paralle<br>Paralle<br>Notes          | roduct       9         ors       9         g networks       10         el prefix       10         el prefix on large arrays       10         on performance       10         Dot product       10                               | 89<br>91<br>94<br>00<br>02<br>06<br>08             |

|   | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul> | Dot pr<br>Merge<br>Sortin<br>Paralle<br>Paralle<br>Notes<br>6.7.1 | roduct       9         rs       10         g networks       10         el prefix       10         el prefix on large arrays       10         on performance       10         Dot product       10         Mergers       10      | 89<br>91<br>94<br>00<br>02<br>06<br>08<br>08<br>08 |

|   | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul> | Dot pr<br>Merge<br>Sortin,<br>Paralle<br>Notes<br>6.7.1<br>6.7.2  | roduct       9         g networks       10         el prefix       10         el prefix on large arrays       10         on performance       10         Dot product       10         Mergers       10         Sorters       10 | 89<br>91<br>94<br>00<br>02                         |

vii

| 7                                       | Related work 1                                             |                                         |                         | 113   |

|-----------------------------------------|------------------------------------------------------------|-----------------------------------------|-------------------------|-------|

|                                         | 7.1                                                        | .1 Embedded GPGPU programming languages |                         |       |

|                                         |                                                            | 7.1.1                                   | Accelerator             | . 113 |

|                                         |                                                            | 7.1.2                                   | Accelerate              | . 114 |

|                                         |                                                            | 7.1.3                                   | Nikola                  | . 115 |

|                                         | 7.2 Embedded languages for graphics and image manipulation |                                         |                         |       |

|                                         |                                                            | 7.2.1                                   | Pan                     | . 116 |

|                                         |                                                            | 7.2.2                                   | Vertigo                 | . 116 |

|                                         |                                                            | 7.2.3                                   | PyGPU                   | . 117 |

|                                         | 7.3 Embedded languages                                     |                                         | . 117                   |       |

|                                         |                                                            | 7.3.1                                   | Lava                    | . 117 |

|                                         |                                                            | 7.3.2                                   | Feldspar                | . 118 |

| 7.4 Data-parallel programming languages |                                                            | parallel programming languages          | . 118                   |       |

|                                         |                                                            | 7.4.1                                   | NESL                    | . 118 |

|                                         |                                                            | 7.4.2                                   | Data parallel Haskell   | . 119 |

|                                         | 7.5 C/C++ based approaches to GPGPU                        |                                         |                         |       |

|                                         |                                                            | progra                                  | $\operatorname{amming}$ | . 119 |

|                                         |                                                            | 7.5.1                                   | CUDA                    | . 119 |

|                                         |                                                            | 7.5.2                                   | OpenCL                  | . 119 |

|                                         | 7.6                                                        | Concl                                   | usion                   | . 119 |

| 8                                       | Cor                                                        | nclusio                                 | 'n                      | 121   |

# List of Figures

| 2.1 | A binary tree summation kernel                                                                                       | 11  |

|-----|----------------------------------------------------------------------------------------------------------------------|-----|

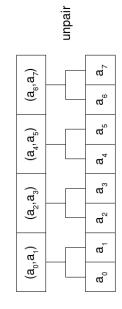

| 4.1 | The functions conc, halve, pair and unpair                                                                           | 24  |

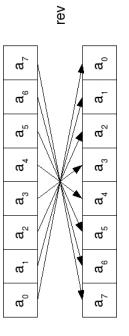

| 4.2 | The functions fmap and rev                                                                                           | 24  |

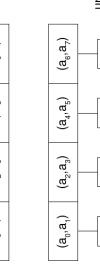

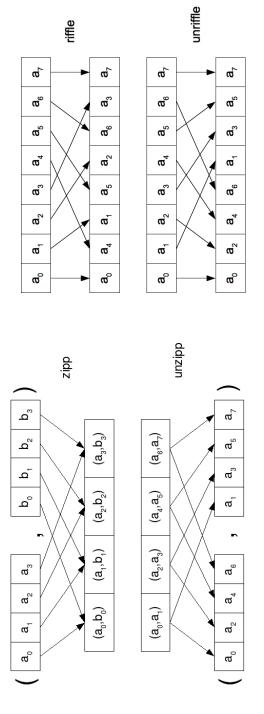

| 4.3 | The functions zipp, unzipp, riffle and unriffle                                                                      | 25  |

| 4.4 | The functions evens (left) and odds (right) $\ldots \ldots \ldots \ldots \ldots$                                     | 27  |

| 4.5 | A selection of functions from the array library $\ldots \ldots \ldots \ldots \ldots$                                 | 29  |

| 4.6 | Example functions on elements                                                                                        | 29  |

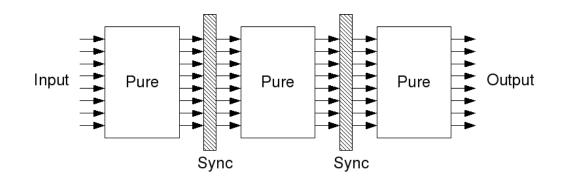

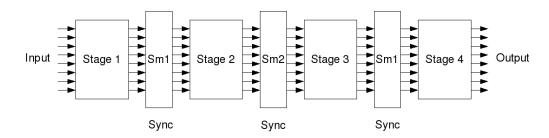

| 4.7 | A GPU Kernel, an object of type a :-> b, can be thought of as some pure computations interspersed by synchronization | 31  |

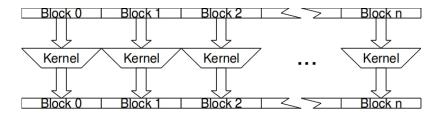

| 4.8 | Many instances of a kernel executed in parallel over blocks of an array.                                             | 33  |

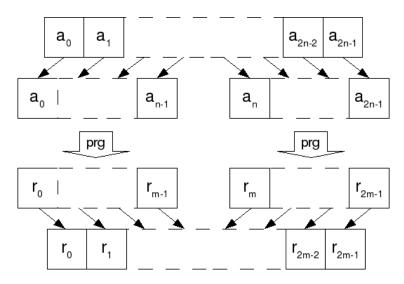

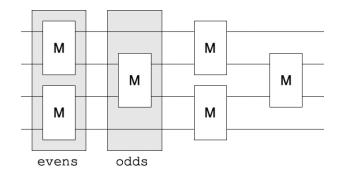

| 4.9 | two, the divide and conquer combinator                                                                               | 46  |

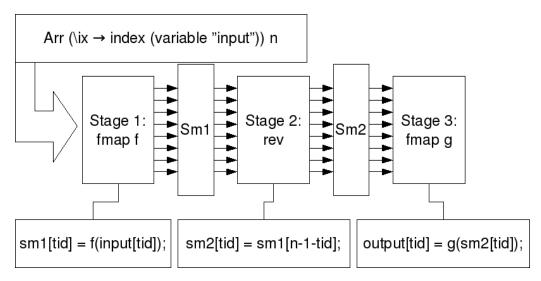

| 5.1 | A Kernel alternately using the arrays sm1 and sm2 for storage                                                        | 80  |

| 5.2 | A sketch of how code is generated for a kernel                                                                       | 83  |

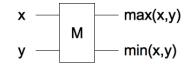

| 6.1 | Small merging network                                                                                                | 95  |

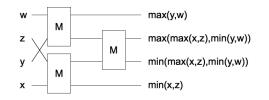

| 6.2 | A four input merging network                                                                                         | 95  |

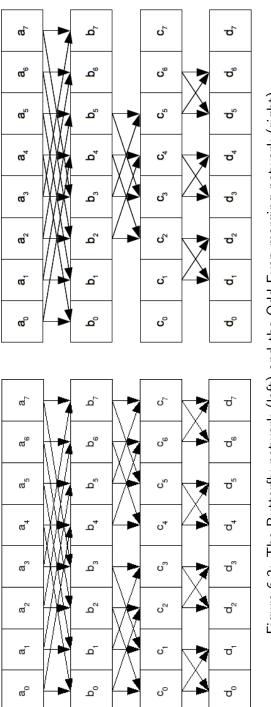

| 6.3 | The Butterfly network (left) and the Odd-Even merging network (right).                                               | 99  |

| 6.4 | A four input version of odd-even transposition sort                                                                  | 101 |

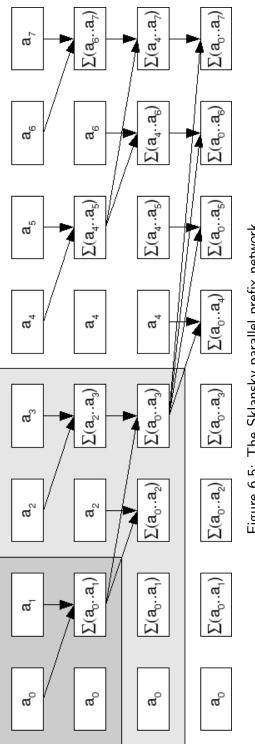

| 6.5 | The Sklansky parallel prefix network                                                                                 | 105 |

## Chapter 1

## Introduction

## 1.1 Graphics Processing Unit: Supercomputer on a PCIe card

Graphics Processing Units (GPUs) today are many-core processors with floating point capabilities in the teraflop range. The performance development of GPUs is driven by the requirements of the graphics used by modern games. Many-core denotes a chip with a high number of small simple processing elements suitable for the fine grained data-parallelism typical of graphics applications. Current GPUs have several hundreds of processing elements on a single chip. For example, The NVIDIA Fermi based GPUs come in models of up to 512 processing elements [27]. The number of processing elements per chip will most likely keep increasing at a high rate. Lately there has been a shift in focus of processor design from single threaded performance to multithreaded performance. For more information on this development see [14, 23, 6].

The computing power available in GPUs makes them interesting in areas other than graphics as well. Even before there were proper tools for general purpose programming on GPUs, people used the graphics APIs in clever ways to exploit the GPU for non-graphics algorithms [28]. In 2006 NVIDIA created CUDA (Compute Unified Device Architecture) that provided a proper tool set for general purpose programming on their GPUs [24]. Using GPUs as data-parallel computing devices is a popular trend which can be seen by the number of languages and tools that have appeared in order to make use of them. Following CUDA, OpenCL arrived. OpenCL is an open API for general purpose programming that can be used with both NVIDIA and AMD GPUs. OpenCL can also be implemented independently of operating system [19]. DirectCompute is also an API for general purpose programming on GPUs DirectCompute is part of the Microsoft DirectX API.

## 1.2 Obsidian: Embedded language for GPU computing

This thesis describes the implementation of Obsidian. Obsidian is an domain specific language for general purpose programming on GPUs. Obsidian is implemented as an embedded language using Haskell as host. The goal of Obsidian is to raise the level of abstraction of GPU programming and offer the programmer a tool that encourages experimentation. From the higher level descriptions, CUDA code is generated.

## **1.3** Research questions

- CUDA is a huge improvement for the GPU programmer. However, there are some quirks that limit the compositionality of CUDA programs. Can an embedded language improve upon this situation while maintaining some of the low level control needed for performance?

- What are the useful combinators (higher order functions) for GPGPU programming and is it possible to generate efficient code for these?

- Can combinators and a "connection pattern" mode of thought borrowed from hardware description be used to alleviate the kind of indexing computations that are ubiquitous in CUDA and similar data-parallel programming models?

- Details of a kernel's implementation, such as number of threads used, should be easily configurable by the programmer with minimum rewriting of code. Can an embedded language approach provide help here?

## 1.4 Structure of this thesis

**Chapter 1** contains an informal introduction to the area and a description of what is to come in the following chapters. In this chapter a number of research questions are posed.

**Chapter 2** is an introduction to the GPGPU area with a section developing a small program in CUDA. This chapter also gives reference to other sources of information on GPGPU programming and tools.

**Chapter 3** contains an introduction to the embedded language approach to solving problems.

**Chapter 4** explains programming in Obsidian. In a series of examples the language features are introduced and used.

Chapter 5 shows two different implementations of Obsidian.

**Chapter 6** contains a few larger examples developed in Obsidian together with some performance measurements.

**Chapter 7** presents related work. Important influences as well as competing approaches to GPGPU programming are treated in this chapter.

**Chapter 8** is the closing chapter where conclusions and reflections upon this work are presented.

## Chapter 2

# General purpose computations on GPUs

### 2.1 Introduction

As graphics processors (GPUs) became more programmable, the desire to utilize their parallel processing power for non-graphics applications arose. At first people wanting to use GPUs for general purpose computations (GPGPU) had to express their problem as a computer graphics computation. This was both limiting in what was expressible and hard. The data to use as input was stored in textures (two dimensional arrays optimized for image storage) and the algorithm to compute on that data expressed using OpenGL or DirectX (the two leading Graphics APIs). For a more in depth description of early (pre 2006) GPGPU methods see [28].

## 2.2 NVIDIA CUDA

The programmability and performance of GPUs kept rising and in 2006 NVIDIA released the 8800GTX graphics card. The 8800GTX graphics card was the first card with a unified GPU architecture released by NVIDIA [26]. Being a unified architecture means that there is only a single kind of processing core on the chip. This is different from earlier GPUs where there where different kinds of processing elements to process *vertex* and *fragment* data. Vertex and fragment refer to the computer graphics concepts, see for example [1] for more details.

In order to simplify making use of the GPU for general purpose computations, NVIDIA released CUDA at the introduction of their unified GPU architecture. CUDA (Compute Unified Device Architecture) is the name of their programming model for general purpose computations on NVIDIA GPUs [25]. CUDA is a big improvement compared to using the graphics APIs for general purpose programming. The programmer is no longer required to translate the problem into a graphics context. CUDA delivers a C compiler and a set of of tools and libraries for general purpose parallel programming on NVIDIA GPUs.

The NVIDIA 8800GTX card came with 128 processing elements, 768MB of memory and had a theoretical peak single precision floating point capability of 518.4 gigaflops [26].Today, in 2010, NVIDIA's top graphics card has 4 times the processing elements (in a single chip) and double the amount of memory.

#### 2.2.1 CUDA architecture

A CUDA enabled GPU comes with a number of multiprocessors. Each multiprocessor contains a number of SIMD (Single Instruction Multiple Data) cores, load-store units, special function units and a local, *shared*, memory. The local memory per multiprocessor is called shared memory because it is used to share data between threads running on a multiprocessor. The number of SIMD cores per multiprocessor is today either 8 or 32 depending on GPU series. The latest version of the CUDA architecture is called Fermi and GPUs based on this architecture have 32 SIMD cores per multiprocessor [27]. The number of multiprocessors in a GPU chip ranges from 1 to 16 today. Thus the number of SIMD processing elements is in the range 8 to 512.

The shared memory per multiprocessor is configurable up to 48KB on Fermi and a fixed 16KB on previous generations. Each multiprocessor also has a number of registers, 32768x32bit registers on Fermi and half that amount in the previous generations.

On the graphics card there is also a *global* memory accessible by all multiprocessors. This global memory, which is often referred to as "device memory", is today in the area of 1GB in size. There are also computing platforms built around the CUDA enabled GPU specifically for general purpose computations. These devices usually come with a larger global memory (4 GB).

The resources available in a multiprocessor determine the maximum number of threads that can be maintained at any one time by that multiprocessor. On Fermi that number is 1024; for earlier generations it is 512. Now, 512 and 1024 are both numbers greater than the number of SIMD cores per multiprocessor. The threads are scheduled on those SIMD cores, maintained by a per multiprocessor scheduler. Groups of 32 threads are executed simultaneously on the the SIMD cores. These groups of 32 threads are called *warps*. Now, 32 is also a number larger than the 8 processing units available. These 32 threads are executed interleaved. threads 0 through 7 execute instruction 1 then threads 8 through 15 execute instruction 1 and so on.

#### 2.2.2 CUDA programming model

The CUDA programming language is based on C but with a small set of language extensions for parallelism and synchronization. In CUDA, problems are solved by specifying a hierarchy of threads. This hierarchy of threads mirrors the architecture. The hierarchy consists of threads that belong to *Blocks* that are part of a *Grid*.

#### Blocks

Since a CUDA enabled GPU can come with varying numbers of multiprocessors, programs needs to be specified in a way that scales with the number of multiprocessors [25]. This leads to a concept exposed to the programmer called *blocks*. A block is a group of threads, at most 512 (1024 on Fermi), that cooperate in solving some subproblem. A block of threads is executed in one multiprocessor and the threads of the block may communicate using shared memory. Each block executes completely independently from any other block, thus giving the desired scalability effect. If there are more multiprocessors available the system simply launches more blocks in parallel. If there is only a single multiprocessor, all blocks will be executed in sequence. The program that is executed by a block is called a *kernel*. The kernel programming model is based in the Single Program Multiple Data (SPMD) paradigm. The kernel is a single program parameterized by a thread identity.

A block of threads can be specified to have one, two or three dimensions. This influences how threads are identified within that block. Threads are given an identity called **threadIdx** that is a three dimensional vector. The three dimensions of the identity are accessed as **threadIdx.x**, **threadIdx.y** and **threadIdx.z**. The maximum sizes of a block in x, y and z is 512, 512 and 64. However, the value x\*y\*z must not be larger than 512 (1024 on Fermi). The kernel program may use the thread identity and conditionally chose one path or another. If this happens in such a way that threads within the same warp chooses different paths these execution paths will execute in sequence, not in parallel. This is a result of the SIMD style execution of the threads within a warp.

There is also a vector called **blockDim** that informs a thread of the size of the block it is part of.

The warp concept mentioned in section 2.2.1 is related to the notion of blocks in the sense that all blocks consist of a number of warps. The warp concept is not something the programmer has influence over. The threads of a block are divided into warps so that thread 0 to 31 is one warp, thread 32 to 63 is another and so on. However, knowledge of the number of threads in a warp and how the threads are divided into warps gives opportunity for performance optimizations. For example threads within a warp may communicate using shared memory without using synchronization primitives. This is because the threads of a warp will execute in SIMD style. That is, each thread is at the same point of execution. Threads that belong to different warps need to use a barrier synchronization primitive called **\_\_syncthreads()** to ensure a uniform view of the shared memory.

#### Grid

A grid is a collection of blocks that all execute the same kernel. A block is identified within a grid by a blockIdx vector. One or two dimensional grids may be specified. The maximum number of blocks in any dimension is 65535. So at most 65535\*65535 blocks may be launched simultaneously on the GPU.

A thread can be globally identified within a grid by using the values of threadIdx, blockDim and blockIdx. This will be shown in section 2.2.3.

#### The host

The host system is the computer that controls the CUDA enabled device. On this system, a controlling CPU thread is in charge of launching grids of blocks on the GPU available to the host. Grids are specified using special CUDA syntax that looks as follows:

```

kernel<<<blocks,threads,sharedmem>>>(arg1, arg2, ..., argn);

```

This launches the kernel called kernel on the GPU in a number of blocks specified by the vector blocks, a number of threads specified by threads and a shared memory

size of sharedmem. The syntax also allows the blocks and threads to be specified using scalars if the grid or block is one dimensional. The arg1, arg2 up to argn are the arguments passed to the kernel. If these arguments are arrays of data, these should reside in the device memory.

The host is also responsible for allocating memory on the device and uploading the data needed to the GPU before launching kernels. Allocating storage in the device memory is done using a cudaMalloc operation and memory transfer to and from the device is done using cudaMemcpy.

#### Programmer view

The CUDA device is a computer system capable of managing a very high number of threads. If it is possible to decompose a problem into pieces that are compatible with the hierarchical thread capabilities of the GPU, the gains can be big. There are reports of speed-ups in the range 10x to 1000x compared to CPU solutions, see for example [24] where a number of success stories are posted.

When a programmer aims to solve a data-parallel programming problem using CUDA, she must decompose the problem into subproblems that can be solved by a grid of blocks. These subproblems must have the characteristic that the data can be divided into chunks that can be computed on completely independently from any other chunk. A kernel is designed that performs the desired computation per chunk. Now, hopefully there is an efficient way to combine the results that this provides per chunk into a solution of that particular sub-problem.

#### 2.2.3 CUDA programming example

In this section, a CUDA program for computing the dot product of two large arrays will be implemented. Computing the dot product has been chosen because it is a simple problem to describe and yet provides room for quite a bit of experimentation in the CUDA implementation. This gives the opportunity to show some of the problems and opportunities presented to the CUDA programmer.

Given two sequences of numbers X and Y of length n, the dot product is given by summing up the all the products  $X_i * Y_i$  for  $i \in 0..(n-1)$ .

A possible implementation of this operations is sequential C code is the following:

```

float dotProduct(float *x, float *y, unsigned int n) {

float r = 0.0f;

for (int i = 0; i < n; ++i) {

r += x[i] * y[i];

}

return r;

}</pre>

```

As the dot product computation is presented above, it is an entirely sequential operation. By splitting this algorithm up into a summing part and a multiplying part, opportunities for parallelization present themselves. Computing each of the products,  $X_i * Y_i$ , can be done completely independently and is easily parallelizable. Computing the products is very easily transformed into CUDA. The naive kernel that performs this operation is completely block size independent. This means that the multiplication kernel can be applied on varying input data sizes without change.

```

__global__ void multKernel(float *result, float *x, float *y) {

unsigned int gtid = blockIdx.x * blockDim.x + threadIdx.x;

result[gtid] = x[gtid] * y[gtid];

}

```

The <u>\_\_global\_\_</u> declaration of the multKernel specifies for the CUDA compiler that this function is a GPU kernel. This kernel takes three pointers as arguments, result, x and y. These pointers point to equal length arrays that reside in the device memory.

The next line computes the global thread id that is used to index into the result and input arrays. If this kernel is used to compute the element wise products of two arrays of length 2000 then 2000 threads are needed to compute all the results. 2000 threads cannot be maintained in a single block, so a multitude of smaller sized blocks must be launched. In this case, the programmer is free to launch for example ten 200-thread blocks to compute the products. This call to multKernel launches ten 200-thread blocks:

```

multKernel<<<10,200,0>>>(r,x,y);

```

Another option would be to launch 100 20-thread blocks to compute the same result. But it is generally not recommended to choose a block size that is smaller than warp size. Even in the 200-threads per block case, the situation is non-optimal. A multiple

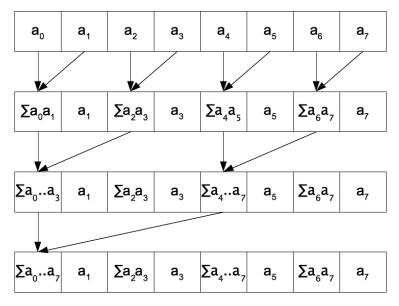

Figure 2.1: A binary tree summation kernel

of warp size would have been better. But forcing the block size to a multiple of warp size would in this case mean the input data would need to have been padded or extra bounds checking code inserted into the kernel. Inserting bounds checking would be impractical because every instance of the kernel would need to execute some extra conditional but only one of them is on the boundary.

Even when implementing this very simple operation as a CUDA kernel there are a number of choices that could have been made differently. The implementation above uses one thread to compute each result. Instead, each thread could compute a number of results but this limits the generality of this kernel. For example, a kernel that computes two results per thread could only be applied to even length arrays.

The second part of the dot product algorithm is to compute the sum of all the elements in the array of results from the multiplication step. This step is not as direct as the previous one and the parallel solution imposes more limitations on input data size than the multKernel did. The summation kernel will use the binary tree shaped approach, as illustrated in figure 2.1. This summation kernel will be applicable to arrays of length a power of two.

The summation kernel will be implemented using one thread per element and the blocks will need to be of size a power of two for proper operation. In order to sum up a large array, larger than the block size, the host must launch further grids to sum up the partial results. This imposes further limitations; for example if an array of size 256\*512 is to be summed up this can be done by launching 256 512-thread blocks followed by a single 256-thread block to get the total sum. But if the array to sum up is 100\*512 elements it is harder to use this kernel to sum up the 100-element partial result. Either this array needs to be padded with zeroes to 128 elements or a specialized kernel that can handle 100 elements would need to be written to take care of that case.

Below is the CUDA code that implements this kernel; it will be explained in detail following the listing:

```

__global__ void sumKernel(float *result, float *x) {

unsigned int tid = threadIdx.x;

extern __shared__ float sm[];

sm[tid] = x[blockIdx.x * blockDim.x + tid];

for (int i = 1; i < blockDim.x; i *= 2) {

__syncthreads();

if (tid % (2*i) == 0) {

sm[tid] += sm[tid + i];

}

}

if (tid == 0) {

result[blockIdx.x] = sm[0];

}

}</pre>

```

The first line specifies that this kernel takes two pointers as arguments, a result array and an input array called  $\mathbf{x}$ . Then a short name for the local thread identity is defined. This kernel will compute sums of block sized arrays in shared memory and during these computations the local thread id will be used to index into that memory. The global thread identity is only used to read in data from the large input array.

The line extern \_\_shared\_\_ float sm[]; names the shared memory array. The size of the shared memory array is set from the host when launching the grid.

Now, data can be read from global memory to local memory using global thread id, sm[tid] = x[blockIdx.x \* blockDim.x + tid];.

The for loop runs log base 2 of the block size times. Each time through the loop a number of threads will perform an addition. In the first iteration block size divided by 2 threads will be active and add up elements, as shown in figure 2.1. The \_\_syncthreads() call is placed in the beginning of the loop so that it acts both as a barrier synchronization between the iterations of the loop and as a barrier between the initial reading of global memory and the first iteration of the loop. The conditional in the loop essentially shuts a number of threads off.

The very last thing this kernel does is writing the sum to global memory. This is done by thread 0. No extra barrier is needed before writing the result to global memory since thread zero will be the one to compute the final iteration through the loop.

Now the multkernel and sumKernel can be used to implement a dot product algorithm. The host code below implements dot product for 128\*512 elements. The block size in use will be 512 and in the multiplication step a 128 block grid is launched. In the summation step two grids will be launched – first a grid of 128 elements and then one containing a single block of 128 threads.

After allocating all device memory and uploading the arrays to GPU memory, the host code would launch the following grids:

```

multKernel<<<128,512,0>>>(device_x,device_x,device_y);

sumKernel<<<128,512,512*sizeof(float)>>>(result, device_x);

sumKernel<<<1,128,128*sizeof(float)>>>(result,result);

```

After executing these grids, the result of the entire computation is stored at index zero in the result array.

#### 2.2.4 Conclusions

CUDA is a huge improvement compared to using graphics APIs for GPGPU programming. This increases programmer productivity and has effect on what can be expressed.

In the previous section a multiplication kernel and a summation kernel were implemented separately. It is, however, possible to implement a fused multiply-sum kernel, which may be desirable for performance purposes.

```

__global__ void mult_sumKernel(float *result, float *x, float *y) {

unsigned int tid = threadIdx.x;

extern __shared__ float sm[];

sm[tid] = x[blockIdx.x * blockDim.x + tid] *

y[blockIdx.x * blockDim.x + tid];

for (int i = 1; i < blockDim.x; i *= 2) {

__syncthreads();

if (tid % (2*i) == 0) {

sm[tid] += sm[tid + i];

}

}

if (tid == 0) {

result[blockIdx.x] = sm[0];

}

}</pre>

```

Another transformation of the sumKernel that may be desirable is to unroll the loops. Unrolling the loops however will impose further input size restrictions.

Section 6.7 shows some running time measurements of the mult\_sumKernel.

There are limitations to how the \_\_syncthreads() barrier can be applied. These limitations are not enforced by the compiler which will gladly compile programs that have unspecified behavior according to the programming manual. For example, syncthreads() can only be used within a conditional if all threads follow the same execution path through it [25].

## 2.3 Other GPGPU programming languages

#### 2.3.1 OpenCL

OpenCL is an open standard for parallel programming designed by the Khronos group [19]. OpenCL offers a programming model very similar to that of CUDA. This section will list the similarities between OpenCL and CUDA and also point out some differences..

14

In OpenCL, just as in CUDA, the programmer specifies a hierarchy of threads (in OpenCL terminology called work-items). Each work-item belongs to a group, a workgroup; corresponding to the CUDA block. The work-group belongs to an NDRange, that corresponds to CUDA's grid. OpenCL also makes the distinction between host and device. The device is a processing unit capable of running OpenCL kernels and the host runs a controlling thread, just as in CUDA.

OpenCL takes things one step further by being less platform bound. An OpenCL application can be executed on a wider range of hardware by utilizing just-in-time compilation. The kernels that make up an application will at runtime be specialized for the kind of hardware that is present in the computer system. Amongst OpenCL enabled devices are GPUs (both NVIDIA and AMD) and multi-core CPUs.

## Chapter 3

# Embedded domain specific languages

## 3.1 Introduction

Embedding domain specific languages within other programming languages is becoming popular. There are many examples of embedded languages in several areas, see chapter 7. An embedded language is implemented as a library within a host language. As a host language, Haskell is a well tested candidate. With Haskell's type class system, the embedded language blends in almost seamlessly.

Domain specific languages (DSLs) are languages that are written to solve problems within a certain domain. Implementing a DSL in the traditional way, as a standalone compiler, may be too expensive in time and effort. Implementing a DSL as an embedded language spares the programmer from implementing the so called frontend part of compiler. The frontend takes care of parsing and lexing, and building the abstract syntax trees that the back-end of the compiler works on [29]. In an embedded language there is a collection of library functions that create the same abstract representations of programs that the frontend usually produces from a source code listing. The embedded language implementor has the choice of implementing an interpreter that computes the result of the program or to embed a compiler. An embedded compiler could, for example, output assembly, virtual machine bytecode or C code.

The presentation of embedded language design and implementation techniques given here borrows extensively from Conal Elliot et al. *Compiliing embedded languages* [12]. That article describes the implementation of an embedded compiler for an image manipulation program called *Pan*.

### **3.2** Abstract syntax

An embedded language is a set of program generating functions in some other language, here Haskell. These programs that are generated need to be represented in some way. One such way to represent programs is as actual source code listings, strings [18]. It is also possible to represent the programs with abstract syntax trees. Below is an example of an expression data type for floating point expressions:

```

data FloatE

```

```

= Var String

| LitFloat Float

| FloatE 'Add' FloatE

| FloatE 'Sub' FloatE

| FloatE 'Mul' FloatE

| FLoatE 'Div' FloatE

| Sin FloatE

| Sqrt FloatE

```

Functions in the embedded language can be represented by Haskell functions over the expression type. For example the function **cos** can be defined as follows:

```

cos :: FloatE -> FloatE

cos theta = Sin (LitFloat 1.5708 'Sub' theta)

```

### 3.3 Syntax

If the programmer using the embedded language were forced to express herself using the constructors of the expression data type, the embedded approach would probably not be popular. Haskell has a system for overloading that becomes very useful in the implementation of embedded languages. This feature of Haskell makes the embedded language blend in elegantly. This is done using the type class system. For example there is a type class called *Num* for basic numeric types. An instance declaration for the expression type looks like this:

```

instance Num FloatE where

(+) a b = a 'Add' b

(-) a b = a 'Sub' b

(*) a b = a 'Mul' b

fromInteger n = LitFloat (fromInteger n)

```

With this *Num* instance and one for *Floating*, that contains amongst other things pi, cosine could be expressed using sine in the following way:

```

\cos \text{ theta} = \sin (\text{pi} / 2 - \text{theta})

```

This is an improvement compared to the first implementation of cosine. In some sense the syntax of the host language is being hijacked and used as syntax for the embedded language.

## 3.4 Inlining

The function, square, in the embedded language, can be thought of as taking a value and giving back its square. As a Haskell function, it generates an expression that contains the Mul constructor and two instances of the input. The definition of square is.

#### square x = x \* x

When applying square to cos t where cos is defined as above and t is a constant, would result in a expression like the one expressed here in mathematical notation:  $\sin(\pi/2 - t) * \sin(\pi/2 - t)$ . The definition of cos has been inlined at both the occurrences of x in the square function. This replication of computations leads to inefficient generated code if not properly taken care of in an optimization phase.

## **3.5** Optimization and smart constructors

The Compiling Embedded Languages [12] article suggests Common Subexpression Elimination (CSE) to improve on the situation with code replication. However, it also explains the use of Smart Constructors to apply some optimizations on the generated code as it is being generated. For example, when implementing the (+) operation for

the embedded language, the inputs to it can be inspected and optimizations applied. If both inputs to (+) are literals of the form LitFloat x, then the generated code does not need to contain any add operation at all.

(+) (LitFloat x) (litFloat y) = LitFloat (x + y)

...

(+) x y = x 'Add' y

In the last case of (+), where x and y are of a form that cannot be processed further, the Add constructor is applied. The ... indicates that there may be many more cases to capture here and some of them may be target architecture specific.

## 3.6 Conclusion

This section introduced the embedded language concept by drawing information from the formative Compiling Embedded Languages paper [12]. The main topic not considered here is the representation and manipulation of typed expressions. An embedded language would most likely have more types than just floating point. This is of course also addressed in [12] where Floats, Ints and Booleans all can be represented in the same expression type. The programmer is given a typed interface though by the use of phantom types [15].

In Pan, images are represented by functions from points (pairs of int expressions) to colors. In order to produce a viewable image, this function needs to be applied at every point in a grid (pixels). C code can be generated that does this by applying the image function to a pair of symbolic points (variable expressions, Var "x" and Var "y") and using the result as the body of a nested for loop that traverses the grid.

The main benefit of the embedded language approach is the effort saved in implementation. There is no need to implement a compiler frontend. A large part of DSL implementation is experimentation and trial and error concerning what features to include and in what way. Being able to perform this cycle of feature implementation and rejection in an embedded language is preferable from a productivity point of view.

## Chapter 4

## Obsidian

### 4.1 Introduction

Obsidian is an embedded language for implementation of GPGPU kernels. The goals of Obsidian is to give the programmer a higher level and more compositional language in which to express GPU kernels. From the higher level descriptions of GPGPU kernels, CUDA code is generated.

Obsidian consists of three parts. First of all there is a collection of operations that can be performed on scalar types. In this category you find, as usual, operations such as , + , -, \* and /. On top of that Obsidian supplies *arrays*. The decision was made to let the length of these arrays specify the degree of parallelism. When generating CUDA code from an Obsidian description, each element of the resulting array is computed by one thread. In the case of nested arrays, the top level array in the nesting specifies the degree of parallelism and the inner arrays are computed sequentially. With the arrays, Obsidian also supplies a library of functions on these arrays. Lastly, there is the third part, a set of operations (combinators) used to construct kernels and guide the code generation.

## 4.2 Array language

This section contains examples of functions from the array language part of Obsidian. The array language consists of a an Array type **Arr a** and a collection of functions on arrays. The Array language programs cannot by themselves be executed on the GPU. Instead, the array language programs need to be turned into GPU kernels using the tools presented in section 4.4.

In Obsidian, an array is represented by an indexing function and a length.

data Arr a = Arr (IndexE -> a) Int

The length of the array is held in a Haskell Int and is static (not subject to change during runtime). The length being static enables some optimizations that will be explained later, see section 5.4.4. The IndexE type represents 32bit unsigned integers. This will be explained in more detail in section 5.

Obsidian arrays can contain elements that are booleans, 32bit floating point numbers or 32bit integers. Since Obsidian in the end is compiled into CUDA, booleans will be represented by 32bit integers. The arrays can also contain tuples or arrays and nesting thereof.

One of the most basic operation that can be performed on an array is to map a function over it. This operation is data-parallel and is of course the first one added into the library:

fmap :: (a  $\rightarrow$  b)  $\rightarrow$  Arr a  $\rightarrow$  Arr b

The fmap function can be used to write a program that increments every element of an array:

incr = fmap (+1)

Another operation on arrays that springs to mind is **foldr**:

foldr :: (a  $\rightarrow$  b  $\rightarrow$  b)  $\rightarrow$  b  $\rightarrow$  Arr a  $\rightarrow$  b

An example use of foldr is to sum up an array. Given an array with the elements  $\{1,2,3,4,5,6\}$ , foldr with the operation + and the the value 0 is (1+(2+(3+(4+(5+(6+0))))))). The standard Haskell foldr on lists can be defined like this:

foldr :: (a -> b -> b) -> b -> [a] -> b

foldr \_ z [] = z

foldr f z (x:xs) = f x (foldr f z xs)

As can be seen from the example above, foldr is a sequential computation. The array language implementation of foldr is also entirely sequential but this is not a problem. Being able to use both sequential and parallel operations in combination is useful when implementing algorithms for GPUs.

In the array language there are many functions that Obsidian inherits from Lava. Lava is a domain specific embedded language for hardware description [4]. There is more information about the Lava hardware description language in the related work section 7.3.1. The first two Lava inspired functions are **pair** and **unpair**:

pair :: Arr a -> Arr (a,a) unpair :: Choice a => Arr (a,a) -> Arr a

The function **pair** takes an array of even length and returns an array of pairs where the first element is paired up with the second, the third with the forth and so on. The **unpair** function does the opposite, see figure 4.1.

|                   | fmap f |                                |  |

|-------------------|--------|--------------------------------|--|

| $\mathbf{a}_7$    |        | $fa_7$                         |  |

| ອ                 | -      | fa。                            |  |

| a₅                |        | fa₅                            |  |

| $\mathbf{a}_{_4}$ |        | fa₄                            |  |

| a                 |        | a <sub>2</sub> fa <sub>3</sub> |  |

| $\mathbf{a}_2$    |        | $fa_2$                         |  |

| a                 |        | f a,                           |  |

| ື່                | -      | $\mathbf{f}  \mathbf{a}_{_0}$  |  |

Figure 4.3: The functions zipp, unzipp, riffle and unriffle

The Choice class contains those types that have an ifThenElse function defined on them:

ifThenElse :: Choice a => BoolE -> a -> a -> a

There is also a function ?? defined that chooses either the first or the second element of a tuple depending on a condition. This can be used to implement a program that replaces every occurrence of a specific element in an array by some given constant:

condReplace e c = fmap ( $x \rightarrow (x ==* e ?? (c,x))$ )

Using the functions pair, fmap and unpair, two higher order functions, pairwise and evens, can be defined. pairwise is takes a two input function and applies it to pairs of an array:

```

pairwise :: (a \rightarrow a \rightarrow b) \rightarrow Arr a \rightarrow Arr b

pairwise f = fmap (uncurry f) . pair

```

The function uncurry used in the implementation of pairwise is a higher order function that takes a function of type  $a \rightarrow b \rightarrow c$  and the result is a function that takes a pair (a,b) as input and produces a c.

evens is similar to pairwise but requires the function to be a two input/two output function:

```

evens :: Choice a => ((a,a) -> (a,a)) -> Arr a -> Arr a

evens f = unpair . fmap f . pair

```

In the implementation of evens above, Haskell function composition (.) is used.

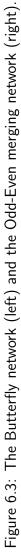

There is also a function called odds that is very similar to evens except that it lets the first and the last element of the array pass through unchanged. The functions odds behaves just like evens on the remaining elements of an array. Figure 4.4 illustrates evens and odds on six inputs. The odds function is a bit more complicated to implement. A way to pass the first and the last element of an array through unchanged is needed, and doing so using as few conditionals as possible. The implementation of the odds function is shown in chapter 5.

In chapter 6, Obsidian will be used to implement sorting networks. One building block that is useful when constructing sorting networks is **sort2**. Given an array of

Figure 4.4: The functions evens (left) and odds (right)

even length, sort2 gives an array where the elements at index 0 and 1 are sorted, the elements at index 2 and 3 are sorted and so on. For example if the input array is  $\{1, 0, 4, 5, 3, 2\}$  the result is  $\{0, 1, 4, 5, 2, 3\}$ .

The sort2 function can easily be implemented using evens given that we have a *compare and swap* operation, cmp:

cmp :: (Choice a , Ordered a) => (a, a)  $\rightarrow$  (a, a) cmp (a, b) = (min a b, max a b)

Now sort2 can be implemented as:

sort2 = evens cmp

The Ordered class provides a set of comparison functions:

(<\*) :: Ordered a => a -> a -> BoolE

(<=\*) :: Ordered a => a -> a -> BoolE

(>\*) :: Ordered a => a -> a -> BoolE

(>=\*) :: Ordered a => a -> a -> BoolE

Two other examples of functions from the array library are zipp and unzipp, see figure 4.3. These two functions are very similar to the Haskell zip and unzip functions on lists:

zipp :: (Arr a, Arr b) -> Arr (a, b)

unzipp :: Arr (a, b) -> (Arr a, Arr b)

As an example, zipp and fmap can be used to implement the well known zipWith function:

```

zipWith :: ((a,b) -> c) -> (Arr a,Arr b) -> Arr c

zipWith f = fmap f . zipp

```

The functions zipp and zipWith here are uncurried. The Haskell counterparts are curried. The reason for this is related to the choice to have array lengths define the number of threads. Working with pairs is a common operation when using Obsidian.

Some functions in the array library only rearrange the elements of an array. These functions could be called permutation functions. An example of a permutation is **rev** that takes an array and reverses the order of the elements, see figure 4.2:

rev :: Arr a -> Arr a

There are also two functions called **riffle** and **unriffle**, figure 4.3. These are also justified by their usefulness in sorting networks:

riffle :: Arr a -> Arr a unriffle :: Arr a -> Arr a

The function **riffle** can be implemented using **halve** that splits an array down the middle into two arrays, **zipp** and **unpair**:

```

riffle :: Arr a -> Arr a

riffle = unpair . zipp . halve

```

Chapter 5 also shows an alternative implementation of **riffle** that is more efficient on a GPU.

The functions described so far are part of the array library of Obsidian. These functions are in some sense the building blocks of which programs are constructed. Most of the functions shown have been motivated by their usefulness in sorting network implementation. As we explore more applications, there will surely be more functions added to the library. In this section, there has been very little talk about parallelism and how these programs are supposed to be executed on a GPU, but this is deliberate. Section 4.4 will go into how GPU kernels are constructed using these building blocks, and some new ones.

```

rev :: Arr a -> Arr a

fmap :: (a -> b) -> Arr a -> Arr b

foldr :: (a -> b -> b) -> b -> Arr a -> b

pair :: Arr a -> Arr (a,a)

unpair :: Choice a => Arr (a, a) -> Arr a

halve :: Arr a -> (Arr a, Arr a)

split :: Int -> Arr a -> (Arr a, Arr a)

conc :: Choice a => (Arr a, Arr a) -> Arr a

zipp :: (Arr a, Arr b) -> Arr (a, b)

unzipp :: Arr (a, b) -> (Arr a, Arr b)

riffle :: Arr a -> Arr a

unriffle :: Arr a -> Arr a

singleton :: a -> Arr a -> Arr (Arr a)

```

Figure 4.5: A selection of functions from the array library

(??) :: Choice a => BoolE -> (a, a) -> a

(==\*) :: Equal a => a -> a -> BoolE

(<\*) :: Ordered a => a -> a -> BoolE

min :: Ord a => a -> a

max :: Ord a => a -> a

Figure 4.6: Example functions on elements

### 4.3 Notes on recursion

Defining functions by means of recursion is very useful. However, when implementing Obsidian array functions or kernels the programmer should be aware that it might lead to code size explosion. This is a typical problem in embedded languages, and is related to how definitions are inlined [12]. Recursion and function application in general take place entirely in the Haskell world and will be completely gone in the resulting generated code. What is left in the generated code is a completely unrolled and inlined version of the computation.

The Haskell recursion should be viewed as a tool for program generation for the Obsidian programmer. Recursion is a very useful tool and should be applied, but with some care. The programmer should be aware that a recursive call to a function in Obsidian will result in CUDA code with the body of that function inlined. There will be many examples of this use of recursion as a code generation tool in the coming sections.

### 4.4 GPU kernels

Section 4.2 showed how to express functions on arrays in Obsidian. This section goes into how these array functions can be mapped onto the GPU in different ways. It is in the language described in this section that parallelism and whether to share computed values or recompute them becomes expressible.

A GPU kernel in Obsidian is represented by a data type a : -> b. This type can be thought of as a program taking an a as input and producing a b. The kinds of kernels that can be represented in this type are illustrated in figure 4.7. This figure shows a program that performs some computation using a number of threads followed by a barrier synchronization, and so on. The boxes marked with *Pure* can be thought of as containing an array program like those in section 4.2.

### 4.4.1 Pure

One basic way to create a new GPU kernel is to take a given array language program, such as incr = fmap (+1), from the previous section. This program increments every element of an array. This array language program can be turned into a GPU kernel by using the function pure:

Figure 4.7: A GPU Kernel, an object of type a : -> b, can be thought of as some pure computations interspersed by synchronization

```

incrKernel :: Num a => Arr a :-> Arr a

incrKernel = pure $ incr

```

#### 4.4.2 Execute

A kernel such as incrKernel can be executed on the GPU from within a *GHCI* (the Glasgow Haskell interpreter) session using a function called execute:

```

execute :: (Flatten a, Flatten b) =>

(Arr a :-> Arr b) -> [a] -> IO [b]

```

The class Flatten will be explained in detail in section 5.4, but instances of Flatten are all the types that can be stored in the GPU memory. Examples of types that are in Flatten are IntE, FloatE, BoolE. Arrays and pairs of things that are in Flatten are also instances of Flatten.

Here, execute is used to run the kernel incrKernel on the GPU:

\*Obsidian> execute incrKernel [0..9 :: IntE] [1,2,3,4,5,6,7,8,9,10]

The elements of the Haskell list given to **execute** are used to create an input array to the kernel. Following this, the kernel is executed on the GPU and the result is read back and presented as a Haskell list again.

The code generated from the incrKernel program is presented below. The details of this source code listing are explain below.

```

__global__ void generated(word* input0,word* result0){

const unsigned int tid = (unsigned int)threadIdx.x;

const unsigned int bid = (unsigned int)blockIdx.x;

ix_int(result0,(tid + (10 * bid))) =

(ix_int(input0,(tid + (10 * bid))) + 1);

}

```

The generated CUDA kernel takes two arguments, an array of input words and an array of output words. Words are 32-bit quantities that can be either floating point or integer valued. This kernel uses no shared memory. The result is computed and written directly back into global memory. This generated CUDA code differs from what a CUDA programmer would write by hand mainly in the use of the ix\_int macro for indexing into an array. There is also a macro called ix\_float for accessing elements as floating point data. The generated CUDA code also uses blockIdx.x to calculate the location of the input and output data. This means that many instances of the generated kernel can be run in parallel over blocks of a large input array, as indicated in figure 4.8. The code generated code, it will be described line by line.

The first line specifies the name and inputs to the kernel. This is no different from what a CUDA programmer might write by hand except for the type word used for the input and output pointers:

#### \_\_global\_\_ void generated(word\* input0,word\* result0){

Generated kernels take one or more array as input. These are named input0, input1 and so on. The outputs are named result0, result1 and so on in the same way.